## ECE 150 Digital Logic Design, Fall 2022 Quiz 2, October 12th 2022

## **Problem 1** (10 pts).

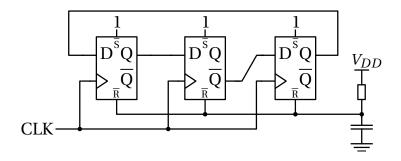

Consider the Mod-N counter in Fig. 1 below. The RC circuit connected to  $\overline{R}$  forces the flip-flops (FFs) to be reset on start-up, hence we know our circuit starts in the 000 state.

- (a) (2 pts) Is this circuit synchronous or asynchronous?

- (b) (6 pts) With FF outputs labeled  $Q_2Q_1Q_0$  left to right, draw a timing diagram to determine the states of the counter.

- (c) (1 pts) Denote the FF states below your timing diagram in decimal, interpreting  $Q_2$  as the MSB and  $Q_0$  as the LSB.

- (d) (1 pts) What Mod is the counter?

Figure 1: Counter circuit with start-up reset configuration.

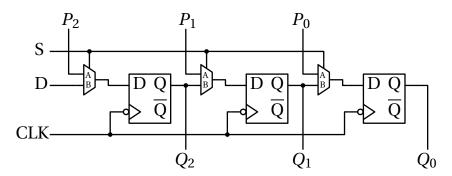

## **Problem 2** (10 pts).

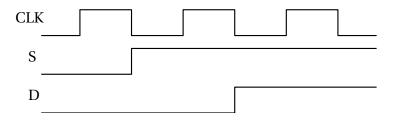

Consider the circuit in Fig. 2, where inputs S and D are also driven by the clock-signal.

Figure 2: 3-bit register with multiplexers.

- (a) (2 pts) Is this circuit synchronous or asynchronous?

- (b) (8 pts) Given  $P_2P_1P_0 = 3_{10}$ , complete the timing diagram below to determine the state of the FFs  $Q_2Q_1Q_0$  at each clock-cycle. Assume the 2:1 muxes select input A when S=0.